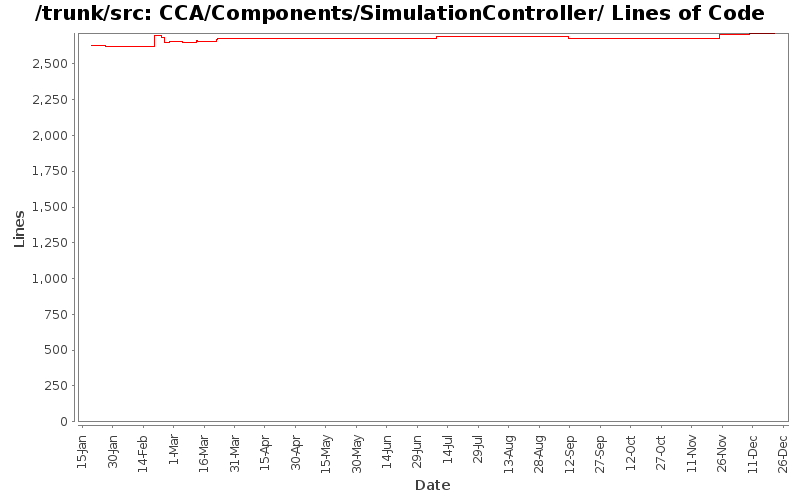

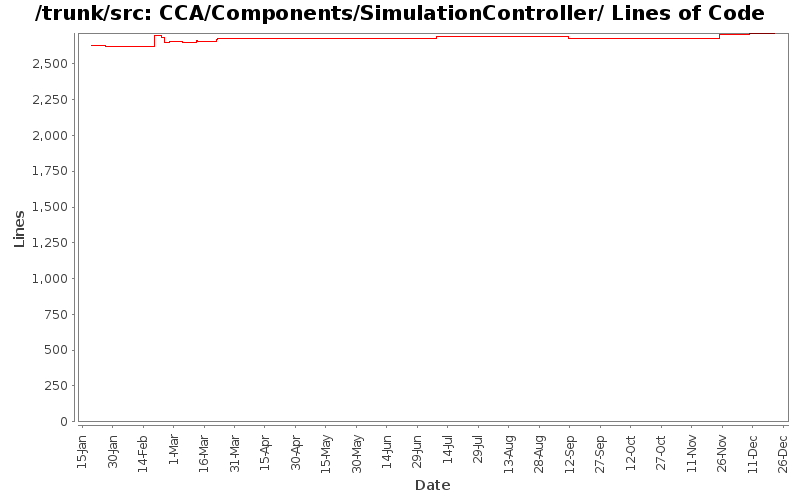

Lines of Code

[root]/CCA/Components/SimulationController

| Author | Changes | Lines of Code | Lines per Change |

|---|---|---|---|

| Totals | 47 (100.0%) | 731 (100.0%) | 15.5 |

| dav | 6 (12.8%) | 411 (56.2%) | 68.5 |

| allen | 26 (55.3%) | 261 (35.7%) | 10.0 |

| harman | 2 (4.3%) | 21 (2.9%) | 10.5 |

| ahumphrey | 4 (8.5%) | 17 (2.3%) | 4.2 |

| tsaad | 3 (6.4%) | 14 (1.9%) | 4.6 |

| jas | 6 (12.8%) | 7 (1.0%) | 1.1 |

more additions to support libsim

0 lines of code changed in 2 files:

added a access method for AMR

0 lines of code changed in 2 files:

correct grid assignment and white space cleanup

12 lines of code changed in 3 files:

added a force regridding option, added access methods to the sim controller, added regridding option to the libsim

82 lines of code changed in 3 files:

Remove antiquated TAU support.

4 lines of code changed in 1 file:

Added method:

bool isRestartInitTimestep()

A component can query the scheduler and determine if it is the initial timestep after

a restart.

AMRSimulationController: run()

- moved

bool first = true;

if (d_restarting) {

d_scheduler->setRestartInitTimestep(first);

}

upstream, before doInitialTimestep().

6 lines of code changed in 1 file:

Ben Isaac, Derek Harris, and Tony Saad: provide a slightly more robust solution to the fix that Ben and Derek proposed for the exploding memory usage on restarts. The fact that there is no legitimate load balancer when (previously) assigning BCs on restarts causes every MPI rank to see all other patches in the domain and assign BCs to all those patches. With the solution committed here, do not assign BCs when the load balancer is NULL. instead, postpone the BC assignment to after the load balancer has been properly set. This commit is 100% backwards compatible and passes the Wasatch RT.

14 lines of code changed in 3 files:

M configure.ac

- Updated test for checking for mpi compiler on BGQ machine.

- I don't have a new enough autoconf on Vulcan so only committing configure.ac... will commit updated configure soon.

M CCA/Components/SimulationController/AMRSimulationController.cc

- Minor syntactic cleanups.

M CCA/Components/SimulationController/SimulationController.cc

- The 'mean' is associated with the 'elap T', so place in (), as opposed to be separated with a comma.

M Core/Grid/Level.cc

- Fix ordering of #includes.

- Line up variables / initialization / etc for easier reading.

- Add some whitespace for easier reading.

- Remove tabs, standarize intention.

- Renamed a few class variables with d_.

- Add {}s.

M Core/Grid/Level.h

- Line up functions so they are easier to find.

- White space, line up variables and functions to make them eaiser to read.

- One line implementations in .h files should be on the same line as function name.

This makes parsing a .h file for member functions much easier.

- grid is now d_grid.

M Core/DataArchive/DataArchive.cc

- Remove debug print for 1000th processor.

258 lines of code changed in 2 files:

Changes required to use c++-11.

1 lines of code changed in 1 file:

additional changes for the libsim and the library search

8 lines of code changed in 1 file:

added better options for using visit

30 lines of code changed in 2 files:

* Add initial infrastructure support for scheduleRestartInitialize().

* This should handle empty scheduleRestartInitialize() { } methods gracefully.

* Some other cleanup while under the hood.

10 lines of code changed in 2 files:

Added scheduleRestartInitialize() to the framework. It's currently disabled, waiting for Alan's mods.

15 lines of code changed in 1 file:

reverted the simstats

11 lines of code changed in 3 files:

added the ability to include a prefix message with the simulation stats

8 lines of code changed in 3 files:

moved the print sim and visit interface to teh end of the while loop

28 lines of code changed in 1 file:

clean up and first iteration for single CPU

0 lines of code changed in 1 file:

This is a recommit of the XML memory usage fix commit that was

committed a month ago (at and around ~r52896), but had a few errors

with respect to a handful of tests (AMR/multi-level?) This has passed

the local RT though there are a few tests that are off by 10e-15 or

so.

M CCA/Components/LoadBalancers/LoadBalancerCommon.cc

M CCA/Components/LoadBalancers/LoadBalancerCommon.h

- Combined a number of pieces of the ParticleLoadBalancer and DynamicLoadBalancer

into LoadBalancerCommon.

- The getOldProcessorAssignment() call previously was implemented in the

CCA/Ports/LoadBalancer.h file, but this was confusing as that should just

be an interface. Placed the 'dynamic' version (used by both Particle and

Dynamic Load Balancers) in this file. Simple and SingleProcessor overwrite

with their own simple version.

- addContribution(), finalizeContributions() resetCostForecaster() and

initializeWeights() are now here (not in the Port LoadBalancer.h

interface anymore) and provide a warning that they actually aren't

doing anything when they are not.

- Removed some old code that was there to read in (old) UDA 1.0s.

- Lined up variables, white space, {}, coding standards, etc.

M CCA/Components/LoadBalancers/DynamicLoadBalancer.h

M CCA/Components/LoadBalancers/DynamicLoadBalancer.cc

M CCA/Components/LoadBalancers/ParticleLoadBalancer.h

M CCA/Components/LoadBalancers/ParticleLoadBalancer.cc

- getPatchwiseProcessorAssignment() and getOldProcessorAssignment() moved into

LoadBalancerCommon.

- Marked a number of 'virtual' functions with the virtual key word.

M CCA/Components/LoadBalancers/SimpleLoadBalancer.h

M CCA/Components/LoadBalancers/SimpleLoadBalancer.cc

M CCA/Components/LoadBalancers/SingleProcessorLoadBalancer.h

M CCA/Components/LoadBalancers/SingleProcessorLoadBalancer.cc

- Implemented getOldProcessorAssignment() here so it would be more clear

where this function is implemented (instead of being buried in the Port interface).

- White space.

M CCA/Components/MPM/ImpMPM.cc

- All cosmetic white space / coding standards updates, with the exception of fixing this bloc:

// Pull out from Time section

d_initialDt = 10000.0;

ProblemSpecP time_ps = restart_mat_ps->findBlock("Time");

if( time_ps ) {

time_ps->get("delt_init",d_initialDt);

}

Added the "if( time_ps )" check. The reason this is necessary is that

the "Time" block no longer exists in the restart_mat_ps portion of the

restart problem spec. (This is due to no longer loading the XML DOM.)

In the above (and previous) code, if "delt_init" is not found, then

10000 is used as a default. [Actually, I'm not quite sure why this is

done, or how this was working, but it 'works' the same now as it did

before.]

M CCA/Components/ProblemSpecification/ProblemSpecReader.h

M CCA/Components/ProblemSpecification/ProblemSpecReader.cc

- Added the readInputFile() function that reads and parses the input UPS file

directly, but does not save the XML DOM (this is done because on huge

simulations with 10Ks of patches, the XML DOM was taking 100s of MB of

memory... now we just get the information out of the file that we need

without saving it).

M CCA/Components/Schedulers/DetailedTasks.h

- Fix naming to use our convention (well, one of them, in this case

the trailing '_' for member variables).

M CCA/Components/Schedulers/DetailedTasks.cc

- Fix indentation, white space.

- Using 'using namespace std' for consistency will all our other .cc files.

M CCA/Components/Schedulers/MPIScheduler.cc

- White space, variable line up.

M CCA/Components/Schedulers/OnDemandDataWarehouse.cc

- Removed the non-used parameters from getOldProcessorAssignment().

- White space, variable line up.

M CCA/Components/Schedulers/SchedulerCommon.h

- Pass strings as const & - don't copy.

M CCA/Components/Schedulers/SchedulerCommon.cc

- Use proc0cout instead of separate if.

- Remove tabs.

M CCA/Components/Schedulers/TaskGraph.cc

- Removed the non-used parameters from getOldProcessorAssignment().

M CCA/Components/Schedulers/UnifiedScheduler.cc

M CCA/Components/SimulationController/AMRSimulationController.cc

- White space.

M CCA/Components/SimulationController/SimulationController.cc

- Line up variables, white space, {}s.

- Renamed "restart_prob_spec" as it is now only the portion of the

restart PS that pertains to the component and thus is now named

"restart_prob_spec_for_component".

M CCA/Ports/LoadBalancer.h

- Organize #includes, white space.

- Make all functions in this interface pure virtual so that they will

be implemented 'closer to home'.

M CCA/Ports/Scheduler.h

- Line up variables, white space, pass strings as const &.

M Core/Containers/HashTable.h

- Move "first()" call into constructor as everywhere in the code when

ever one of these was created, first() was immediately called.

M Core/DataArchive/DataArchive.h

- No longer creating the giant (for 10K+ patches) XML DOM objects.

Instead, parse them directly for the information needed and pass

that around.

- Pass strings as const &.

- White space, capitalization, line up variables, {}s, etc.

- More passing const variables as const.

- d_tsindex becomes the more readable d_ts_index, etc.

- DataArchive needs the Load Balancer now in order to know where patches belong.

M Core/DataArchive/DataArchive.cc

- Organize #includes.

- White space, etc.

- Add UPS file parsing codes for parsing as we stream through the file.

- UDAs (the xml) are actually read in in several phases. Previously because

they were read into an XML DOM data structure, we just passed that around

and it didn't make a difference. Now we have to be smarter about what

is read when.

- Fix the outputting of restart UPS files (previously the old restart information

was lost).

- Renamed variable Url to Filename as that is what it is.

M Core/Grid/Variables/ComputeSet.h

- Fix spacing.

M Core/ProblemSpec/ProblemSpec.h

M Core/ProblemSpec/ProblemSpec.cc

- Added XML parsing via streaming file functions.

- Fix spacing.

- Added constructor that will create a ProblemSpec from data in a buffer.

- This is used when we parse an input UPS file and need (small) parts

of it still as an UPS file (eg, to be passed down to a component

so that we don't have to change component code at this point).

M StandAlone/compare_uda.cc

M StandAlone/tools/compute_Lnorm_udas.cc

- Due to extra linking requirements, we need to init the Uintah Parallel

library before running (even if the initialization just tells the

library that it is not running under MPI) using these calls:

Uintah::Parallel::determineIfRunningUnderMPI( argc, argv );

Uintah::Parallel::initializeManager(argc, argv);

- Fix #includes.

- Coding standard updates.

M StandAlone/sus.cc

- Space out the exception handling to make the code easier to follow.

100 lines of code changed in 2 files:

second round of initial checkins for Uintah and VisIt

8 lines of code changed in 1 file:

first cut to add VisIt's libsim into Uintah - not yet functional

74 lines of code changed in 4 files:

M Regridder/TiledRegridder.cc

M SimulationController/AMRSimulationController.cc

- Cosmetic coding standards updates.

M Schedulers/SchedulerCommon.cc

- Cosmetic white space updates.

M Schedulers/TaskGraph.cc

- Cosmetic fixes, including consistent use of "std::".

M SimulationController/SimulationController.cc

- Cosmetic white space updates, line up variables, etc.

53 lines of code changed in 2 files:

Made the following changes:

1. Compress large xml files. Remove sus log.

2. Add Changelog.

3. Add instructions for adding a new component to the build system.

4. Update OSX build in install documentation.

5. Update petsc version in install documentation.

6. Change Petsc version.

7. Remove references to Teem in installation. Remove the build directory

after creating the tarball for the release.

8. Remove Tracker feature.

9. Remove AIX references. Remove Basis/. Remove Teem. Remove sci_defs

include files related to SCIRun.

10. Remove old build dependency versions.

11. Add wasatch_3P 1.6.0 branch.

12. Remove bench.config file, update excludes when building release tar ball.

13. Remove *.orig and *.release files.

14. Update copyright date. Update version to 1.6.

6 lines of code changed in 5 files:

Significant scheduler cleanup, formatting, { }s.

This is the beginning of a full cleansing of the scheudler class hierarchy, etc.

3 lines of code changed in 1 file: