# A Survey of the Itanium Architecture from a Programmer's Perspective

Christiaan Paul Gribble and Steven G. Parker

## UUSCI-2003-003

Scientific Computing and Imaging Institute University of Utah Salt Lake City, UT 84112 USA

August 30, 2003

## Abstract:

The Itanium family of processors represents Intel's foray into the world of Explicitly Parallel Instruction Computing and 64-bit system design. This survey contains an introduction to the Itanium architecture and instruction set, as well as some of the available implementations. Taking a programmer's perspective, we have attempted to distill the relevant information from a variety of sources, including the Intel Itanium architecture documentation.

In varying levels of detail, we cover the important characteristics of the Itanium architecture, a large portion of the Itanium instruction set, program performance factors and optimizations, and several of the available Itanium implementations. While this survey does not provide exhaustive discussions of these topics, we hope that it will serve as a practical introduction to creating new applications for the Itanium architecture.

# A SURVEY OF THE ITANIUM ARCHITECTURE FROM A PROGRAMMER'S PERSPECTIVE

Christiaan Paul Gribble Steven G. Parker

Scientific Computing and Imaging Institute University of Utah August 2003 Copyright © 2003 Christiaan Paul Gribble and Steven G. Parker All Rights Reserved

# Contents

| 1 | The  | Itanium Architecture 1                                                                               | i        |

|---|------|------------------------------------------------------------------------------------------------------|----------|

| 2 | Inst | ruction Set Architecture 3                                                                           | 3        |

|   | 2.1  | Information Units and Data Types                                                                     | 3        |

|   |      | 2.1.1 Integers                                                                                       | 3        |

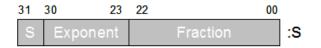

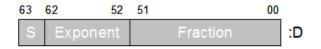

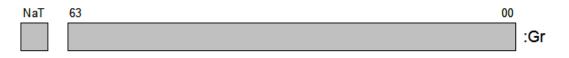

|   |      | 2.1.2 Floating-Point Numbers                                                                         | 3        |

|   |      | 2.1.3 Alphanumeric Characters                                                                        | 5        |

|   | 2.2  | Instruction Formats                                                                                  |          |

|   | 2.3  | Instruction Classes                                                                                  | 5        |

|   | 2.4  | Addressing Modes 7                                                                                   |          |

|   |      | 2.4.1   Immediate Addressing   7                                                                     |          |

|   |      | 2.4.2       Register Direct Addressing       7                                                       |          |

|   |      | 2.4.3       Register Indirect Addressing       7         7       7       7                           |          |

|   |      | 2.4.3       Register induced Addressing       7         2.4.4       Autoincrement Addressing       7 |          |

|   |      |                                                                                                      |          |

| 3 |      | itectural Registers 9                                                                                |          |

|   | 3.1  | Instruction Pointer                                                                                  |          |

|   | 3.2  | General-Purpose Registers                                                                            | )        |

|   | 3.3  | Floating-Point Registers                                                                             | )        |

|   | 3.4  | Branch Registers                                                                                     | l        |

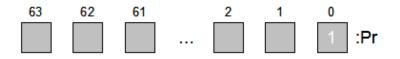

|   | 3.5  | Predicate Registers                                                                                  | 2        |

|   | 3.6  | Application Registers                                                                                | <u>)</u> |

|   | 3.7  | System Information Registers                                                                         | <u>)</u> |

|   | 3.8  | Other Processor Registers                                                                            | 3        |

| 4 | Iton | um Assembler Statements 14                                                                           | 1        |

| 4 | Itan | um Assembler Statements                                                                              | •        |

| 5 |      | ger Instructions 16                                                                                  |          |

|   | 5.1  | Arithmetic Instructions                                                                              |          |

|   |      | 5.1.1 Addition                                                                                       | 5        |

|   |      | 5.1.2 Subtraction                                                                                    | 5        |

|   |      | 5.1.3 Shift Left and Add                                                                             | 5        |

|   |      | 5.1.4 Multiplication and Division of 64-bit Integers                                                 | 7        |

|   |      | 5.1.5 Multiplication of 16-bit Integers                                                              | 7        |

|   |      | 5.1.6 Special-Case Arithmetic Operations                                                             | 3        |

|   | 5.2  | Data Access Instructions                                                                             | )        |

|   |      | 5.2.1 Load Instructions                                                                              | )        |

|   |      | 5.2.2 Store Instructions                                                                             | )        |

|   |      | 5.2.3 Move Long Immediate Instruction                                                                | )        |

|   |      | 5.2.4 Accessing Specialized Registers                                                                |          |

|   | 5.3  | Miscellaneous Integer Instructions                                                                   |          |

|   | 0.0  | 5.3.1 Zero-Extend Instruction                                                                        |          |

|   |      | 5.3.2 Sign-Extend Instruction                                                                        |          |

|   |      | 5.3.3 Instructions for Narrow Data Types                                                             |          |

|   |      |                                                                                                      |          |

| 6 |      | parison and Branching Instructions 22                                                                | _        |

|   | 6.1  | Comparison Instructions                                                                              |          |

|   |      | 6.1.1 Signed Comparison                                                                              |          |

|   |      | 6.1.2 Unsigned Comparison 22                                                                         |          |

|   |      | 6.1.3 Unconditional Comparison                                                                       |          |

|   | 6.2  | Branch Instructions                                                                                  | 3        |

| 7  | Logi                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 25                                                                                                                               |

|----|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

|    | 7.1                                                                                                                      | e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 25                                                                                                                               |

|    | 7.2                                                                                                                      | Bit-Level Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 25                                                                                                                               |

|    |                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 25                                                                                                                               |

|    |                                                                                                                          | e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 26                                                                                                                               |

|    |                                                                                                                          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 26                                                                                                                               |

|    |                                                                                                                          | 7.2.4 Single-Bit Test Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 27                                                                                                                               |

| 0  | ы                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | •••                                                                                                                              |

| 8  |                                                                                                                          | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 28                                                                                                                               |

|    | 8.1                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 29                                                                                                                               |

|    |                                                                                                                          | , , <u>,</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 29                                                                                                                               |

|    |                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 29                                                                                                                               |

|    |                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 29                                                                                                                               |

|    |                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 31                                                                                                                               |

|    |                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 31                                                                                                                               |

|    | 8.2                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 31                                                                                                                               |

|    |                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 31                                                                                                                               |

|    | ~ •                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 33                                                                                                                               |

|    | 8.3                                                                                                                      | e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 33                                                                                                                               |

|    |                                                                                                                          | 8 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 33                                                                                                                               |

|    |                                                                                                                          | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 34                                                                                                                               |

|    |                                                                                                                          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 34                                                                                                                               |

|    |                                                                                                                          | 8 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 34                                                                                                                               |

|    |                                                                                                                          | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 35                                                                                                                               |

|    | 8.4                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 36                                                                                                                               |

|    |                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 36                                                                                                                               |

|    |                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                  |

|    |                                                                                                                          | 8.4.2 Integer Multiplication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 37                                                                                                                               |

| 0  | Doro                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                  |

| 9  |                                                                                                                          | lel Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 38                                                                                                                               |

| 9  | 9.1                                                                                                                      | lel Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>38</b><br>38                                                                                                                  |