# HIGH PERFORMANCE MULTISCALE IMAGE PROCESSING FRAMEWORK ON MULTIGPUS WITH APPLICATIONS TO UNBIASED DIFFEOMORPHIC ATLAS CONSTRUCTION

by

Linh Khanh Ha

A thesis submitted to the faculty of

The University of Utah

in partial fulfillment of the requirements for the degree of

$\begin{array}{c} {\rm Doctor\ of\ Philosophy} \\ {\rm in} \\ {\rm Computing} \end{array}$

School of Computing

The University of Utah

May 2011

Copyright © Linh Khanh Ha2011

All Rights Reserved

## THE UNIVERSITY OF UTAH GRADUATE SCHOOL

# SUPERVISORY COMMITTEE APPROVAL

of a thesis submitted by

#### Linh Khanh Ha

| This thesis has been read by each by majority vote has been found to |        | of the following supervisory committee and sfactory. |

|----------------------------------------------------------------------|--------|------------------------------------------------------|

|                                                                      | Chair: | Cláudio T. Silva                                     |

|                                                                      |        | Sarang Joshi                                         |

|                                                                      |        | Jens Krüger                                          |

|                                                                      |        | P. Thomas Fletcher                                   |

|                                                                      |        | Joao Comba                                           |

## THE UNIVERSITY OF UTAH GRADUATE SCHOOL

# FINAL READING APPROVAL

| To the Graduate Council of t                                                               | he University of Utah:                                      |                            |

|--------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------------|

| I have read the thesis of<br>found that:                                                   | Linh Khanh Ha                                               | in its final form and have |

| <ul><li>(1) its format, citations, and</li><li>(2) its illustrative materials in</li></ul> | ncluding figures, tables, and atisfactory to the Supervisor |                            |

| Date                                                                                       | Cláudio T. Silva                                            |                            |

|                                                                                            | Chair, Supervisory Co                                       | mmittee                    |

| ${f Appro}$                                                                                | oved for the Major Depa                                     | rtment                     |

|                                                                                            | Al Davis<br>Chair/Dean                                      |                            |

| Appr                                                                                       | roved for the Graduate C                                    | Council                    |

|                                                                                            | Charles A. Wight                                            |                            |

|                                                                                            | Dean of The Graduate School                                 | 1                          |

#### ABSTRACT

Stochastic methods, dense free-form mapping, atlas construction, and total variation are examples of advanced image processing techniques which are robust but computationally demanding. These algorithms often require a large amount of computational power as well as massive memory bandwidth. These requirements used to be fulfilled only by supercomputers. The development of heterogeneous parallel subsystems and computation-specialized devices such as Graphic Processing Units (GPUs) has brought the requisite power to commodity hardware, opening up opportunities for scientists to experiment and evaluate the influence of these techniques on their research and practical applications. However, harnessing the processing power from modern hardware is challenging. The differences between multicore parallel processing systems and conventional models are significant, often requiring algorithms and data structures to be redesigned significantly for efficiency. It also demands in-depth knowledge about modern hardware architectures to optimize these implementations, sometimes on a per-architecture basis.

The goal of this dissertation is to introduce a solution for this problem based on a 3D image processing framework, using high performance APIs at the core level to utilize parallel processing power of the GPUs. The design of the framework facilitates an efficient application development process, which does not require scientists to have extensive knowledge about GPU systems, and encourages them to harness this power to solve their computationally challenging problems. To present the development of this framework, four main problems are described, and the solutions are discussed and evaluated: (1) essential components of a general 3D image processing library: data structures and algorithms, as well as how to implement these building blocks on the GPU architecture for optimal performance; (2) an implementation of unbiased atlas construction algorithms—an illustration of how to solve a highly complex and computationally expensive algorithm using this framework; (3) an extension of the framework to account for geometry descriptors to solve registration challenges with large scale shape changes and high intensity-contrast differences; and (4) an out-of-core streaming model, which enables developers to implement multi-image processing techniques on commodity hardware.

# CONTENTS

| ABSTRACT                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | iii                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | vii                                                                                    |

| LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | xii                                                                                    |

| ACKNOWLEDGEMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | xiv                                                                                    |

| CHAPTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                        |

| 1. INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1                                                                                      |

| 1.1 Parallel computing overview 1.1.1 Modern trends in parallel computing 1.1.1.1 Multicore systems 1.1.1.2 Specialized processors 1.1.1.3 Heterogeneous computing 1.1.2 Parallel computing challenges 1.2 GPU computing 1.2.1 GPU computational model 1.3 Atlas construction problem 1.4 Challenges 1.4.1 Baseline research challenges 1.4.2 Efficient implementation challenges 1.5 Contributions                                                                                | 1<br>3<br>4<br>4<br>4<br>6<br>7<br>8<br>10<br>13<br>16<br>16<br>17<br>18               |

| 2.1 Framework overview 2.2 Core methods 2.2.1 Diffeomorphic image registration algorithms 2.2.1.1 Greedy iterative diffeomorphism 2.2.1.2 Large Deformation Diffeomorphic Metric Mapping 2.3 High performance image processing framework on GPUs 2.3.1 Data structures 2.3.1.1 Volume image presentation 2.3.1.2 Vector field presentation 2.3.2 Basic image operators 2.3.2.1 Gradient computation 2.3.3 ODE integration 2.3.4 PDE Solver 2.3.5 Successive over relaxation method | 211<br>233<br>233<br>244<br>266<br>266<br>277<br>277<br>30<br>311<br>322<br>333<br>346 |

|    | 2.3.7 Multiscale framework                 | 37  |

|----|--------------------------------------------|-----|

|    |                                            | 39  |

|    |                                            | 39  |

|    |                                            | 41  |

|    |                                            | 41  |

|    |                                            | 43  |

|    | 1 1                                        | 43  |

|    |                                            | 43  |

|    |                                            | 44  |

|    |                                            | 45  |

|    |                                            | 46  |

|    | *                                          | 47  |

|    | 2.0 Conclusion                             | 1.  |

| 3. | COMBINING PROBABILISTIC AND GEOMETRIC      |     |

|    | DESCRIPTOR                                 | 49  |

|    | 3.1 Introduction                           | 49  |

|    |                                            | 51  |

|    |                                            | 51  |

|    | *                                          | 53  |

|    |                                            | 55  |

|    | •                                          | 56  |

|    |                                            | 58  |

|    | 1 1                                        | 59  |

|    | e e e e e e e e e e e e e e e e e e e      | 59  |

|    | • •                                        | 63  |

|    | *                                          | 65  |

|    |                                            | 65  |

|    |                                            | 66  |

|    | •                                          | 67  |

|    |                                            | 67  |

|    |                                            | 70  |

|    |                                            | 70  |

|    | 1 0                                        | 7]  |

|    | *                                          | 7]  |

|    | 3.6 Conclusions                            |     |

|    | 5.0 Coliciusions                           | 1 4 |

| 4. | AN OUT-OF-CORE FRAMEWORK FOR               |     |

|    | MULTI-IMAGE PROCESSING                     | 73  |

|    | 4.1 Introduction                           | 73  |

|    |                                            | 75  |

|    |                                            | 77  |

|    |                                            | 77  |

|    |                                            | 80  |

|    | <u>e</u>                                   |     |

|    | v                                          | 8]  |

|    |                                            | 82  |

|    |                                            | 83  |

|    | <u> </u>                                   | 85  |

|    | 4.4.5 Hardware-independent streaming model | 86  |

|               | 4.4.6 Discussion on streaming modes           | 86  |

|---------------|-----------------------------------------------|-----|

|               | 4.5 Reordering stages in streaming models     |     |

|               | 4.5.1 Forced synchronizations                 |     |

|               | 4.5.2 Reordering pipeline stages              | 89  |

|               | 4.6 Extension to a full out-of-core framework | 91  |

|               | 4.7 Results                                   | 92  |

|               | 4.7.1 Full asynchronous processing            | 93  |

|               | 4.7.2 Synchronous functions                   | 94  |

|               | 4.7.3 Regular out-of-core functions           | 95  |

|               | 4.8 Conclusions                               | 97  |

| <b>5</b> .    | CONCLUSIONS AND FUTURE WORK                   | 98  |

| $\mathbf{AP}$ | PENDICES                                      |     |

| Α.            | PARALLEL GPU SORTING                          | .00 |

| В.            | SOFTWARE ARCHITECTURE 1                       | .14 |

| ВF            | FERENCES 1                                    | 25  |

# LIST OF FIGURES

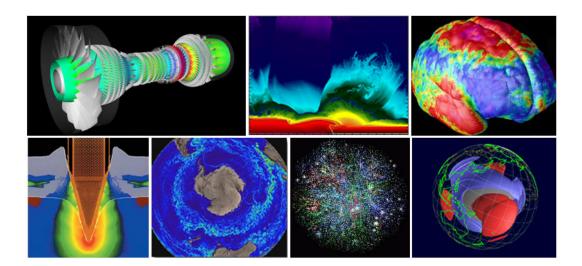

| 1.1 | Parallel computing has been a driving force for the development of many scientific research disciplines and the solution for a number of engineering challenges in domain as diverse as mechanical engineering, nuclear physics, bio-science, applied physics, weather prediction, astronomy, geology, and more (Image courtesy of Blaise Barney, Lawrence Livermore National Laboratory [7]) | 1  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

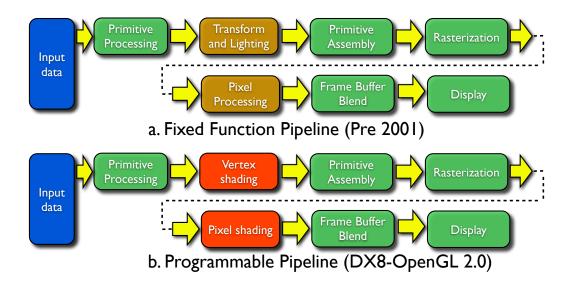

| 1.2 | The development of GPU processing pipeline from a) a fixed function pipeline to b) a programmable pipeline is a prerequisite for General Purpose Computing on GPUs (GPGPUs).                                                                                                                                                                                                                  | 9  |

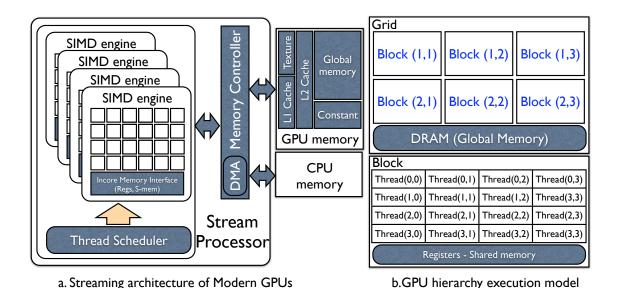

| 1.3 | Hardware architecture and execution model of modern GPUs. Modern GPUs are modeled as stream processors, with a large number of simple, compute centric cores compounded with a high bandwidth parallel memory interface. The multilevel threading hierarchy allows efficient parallel execution model with a fine-grain approach                                                              | 11 |

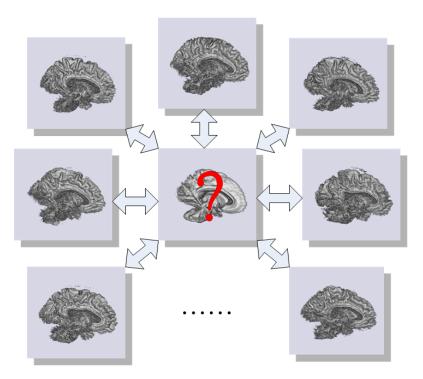

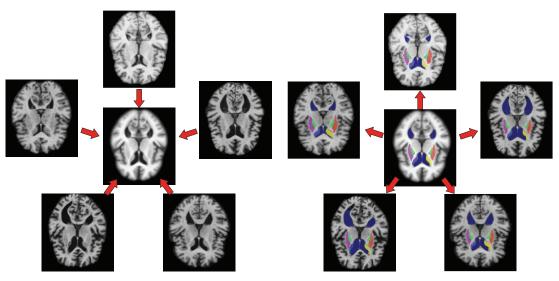

| 1.4 | Brain atlas construction from a population. Here we implement an unbiased atlas construction approach based on averaging in diffeomorphic space                                                                                                                                                                                                                                               | 13 |

| 1.5 | Automatic segmentation via atlas construction. The process includes two steps: a) Construct the brain atlas from the population - determine the mapping between each image and the atlas. b) Partition the atlas - the segmentation on an individual is done automatically via a reverse mapping from the atlas                                                                               | 14 |

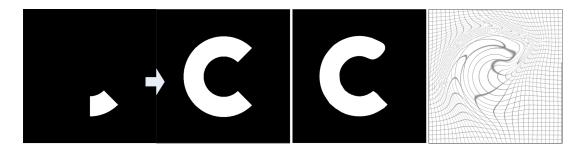

| 1.6 | A small part of the letter "C" deforming into a full "C" using 2D Greedy Iterative Diffeomorphism. From left to right: 1. Input and Target Image 2. Deformed template. 3. Grid showing the deformation applied to template.                                                                                                                                                                   | 15 |

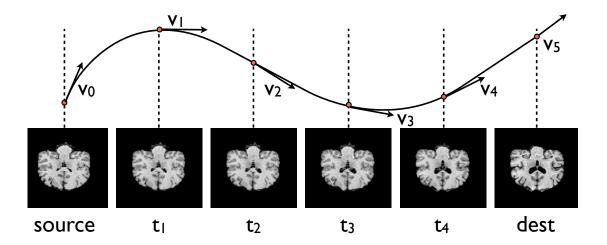

| 2.1 | Forward itergration of the vector field in Greedy Iterative matching                                                                                                                                                                                                                                                                                                                          | 23 |

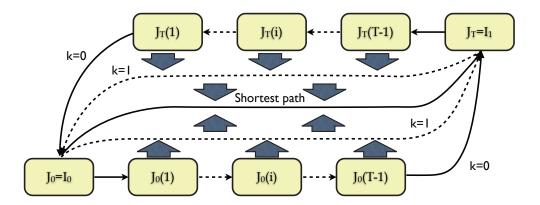

| 2.2 | LDDMM estimate the transformation based on both forward and backward integration of vector field in two opposite directions between the source and the target                                                                                                                                                                                                                                 | 25 |

| 2.3 | The computation runtime of basic GPU functions is linearly proportional to the size of the input data. We also observe the similar trends with other GPU functions, it explain why a tight volume presentation is generally preferred in our framework                                                                                                                                        | 27 |

| 2.4 | Vector field presentation and one-D optimization for vector field computation                                                                                                                                                                                                                                                                                                                 | 28 |

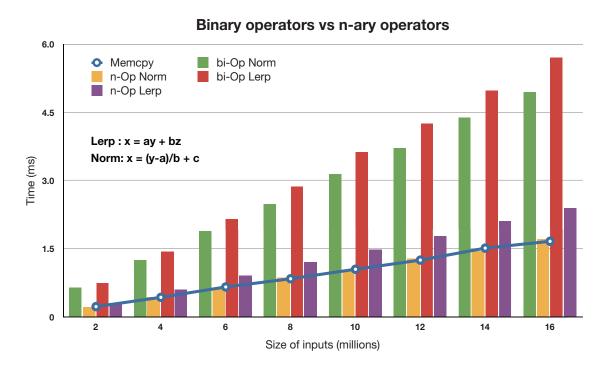

| 2.5  | n-ary versus classic binary operator with linear interpolation and range normalization function. We use the memory copy from device to device, in other words, a no-op function as reference to show the optimality of our n-ary approach. Runtime is measured in milliseconds on an NVIDIA GTX                                                                                     |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | 260                                                                                                                                                                                                                                                                                                                                                                                 | 29 |

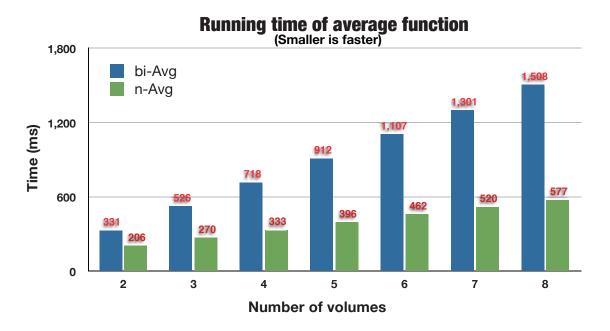

| 2.6  | n-ary average function versus binary average operator                                                                                                                                                                                                                                                                                                                               | 30 |

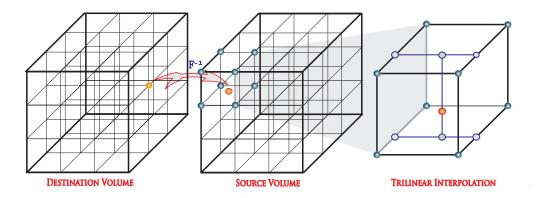

| 2.7  | Reverse mapping based on 3D trilinear interpolation                                                                                                                                                                                                                                                                                                                                 | 31 |

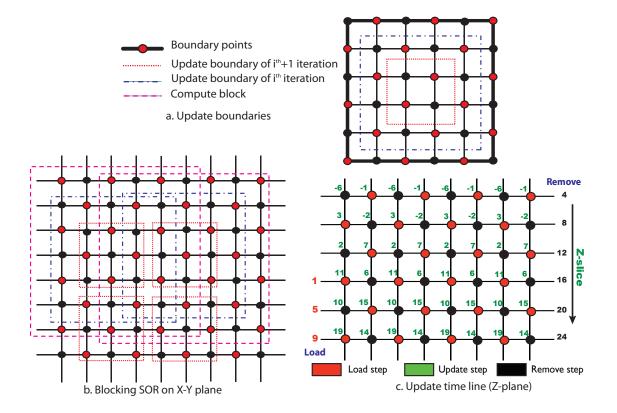

| 2.8  | Parallel block SOR, we assign each CUDA thread warp a block of data to compute the black points inside the blue boundary, and use that result to compute the red point inside the red boundary. Two neighboring compute blocks share a four grid point-wide region                                                                                                                  | 34 |

| 2.9  | CG Solver template                                                                                                                                                                                                                                                                                                                                                                  | 36 |

| 2.10 | Matrix vector multiplication CUDA kernel with implicit Helmholtz Matrix .                                                                                                                                                                                                                                                                                                           | 37 |

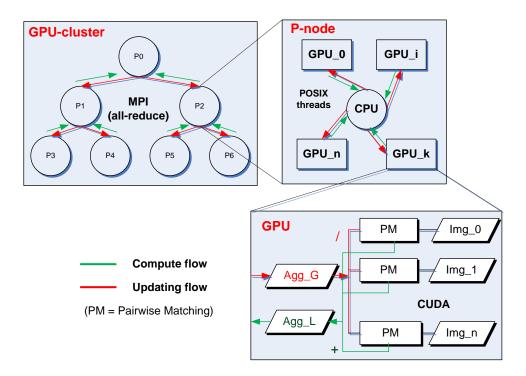

| 2.11 | Multi-GPUs framework on the GPU cluster. We combine the processing models using a hierarchical strategy, from a single-GPU model to a single node multi-GPUs model using PThreads, and finally to a GPU cluster with MPI communication between processing nodes. The distribution of compute flow and the data updating process happens in the opposite direction of the hierarchy. | 40 |

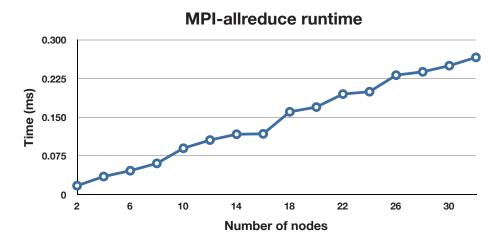

| 2.12 | MPI-All reduce runtime on an infiniband network with OpenMPI 1.3 shows a linear dependency on the number of nodes                                                                                                                                                                                                                                                                   | 42 |

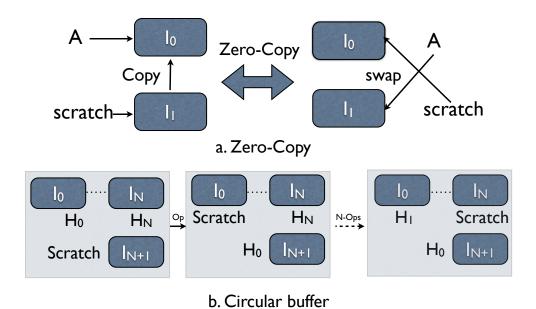

| 2.13 | Optimization strategies with the scratch memory model                                                                                                                                                                                                                                                                                                                               | 44 |

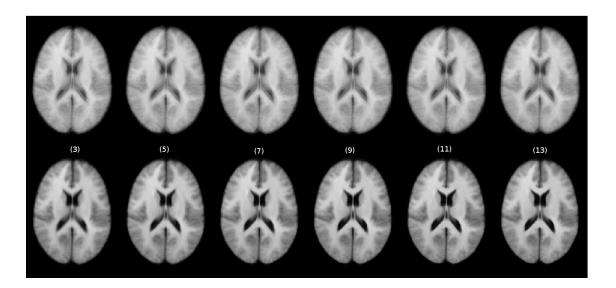

| 2.14 | Atlas results with 3, 5, 7, 9, 11 and 13 inputs constructed by (a) arithmetically averaging rigidly aligned images (top row) and (b) Greedy Iterative Average template construction (bottom row)                                                                                                                                                                                    | 45 |

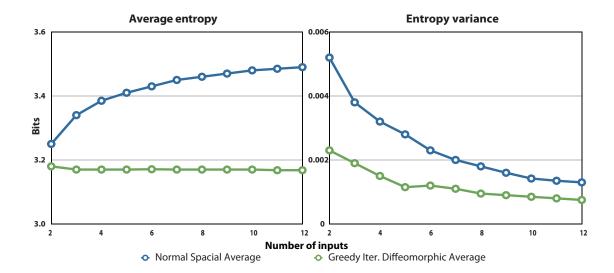

| 2.15 | Mean entropy and variance of atlases constructed by arithmetically averaging and the Greedy Iterative Average template                                                                                                                                                                                                                                                              | 46 |

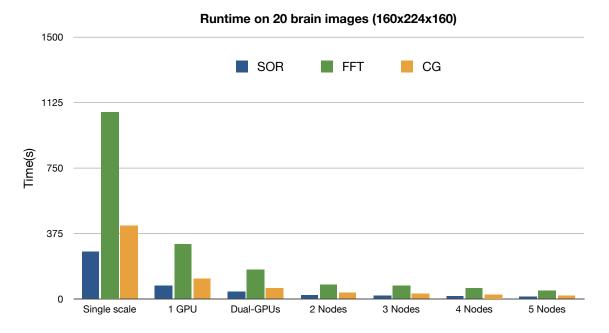

| 2.16 | Runtime to compute the average atlas of the 20 T1 brain images ( $144 \times 192 \times 160$ ) with multiscale and/or multi-GPUs, cluster implementation in reference to one scale version                                                                                                                                                                                          | 47 |

| 2.17 | Multiscale runtime to compute the average atlas of the 315 T1 brain images $(144 \times 192 \times 160)$ with different PDE solver                                                                                                                                                                                                                                                  | 48 |

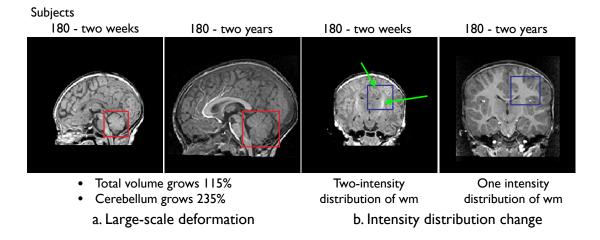

| 3.1  | Registration challenges of human brains at early development stages. The image shows significant shape and size changes of an infant brain of subject 180 from two weeks to two years as well as the changing white matter properties and appearance due to the myelination                                                                                                         | 50 |

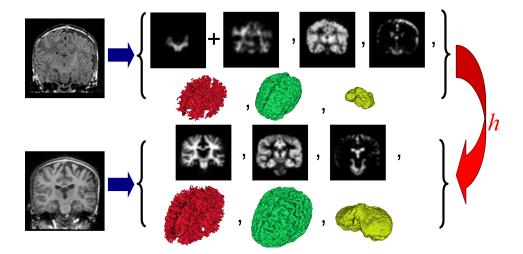

| 3.2  | Overview of the proposed registration method that can handle large deformations and different contrast properties, applied to mapping brain MRI of neonates to 2-year-olds. We segment the brain MRIs and then extract equivalent anatomical descriptors by merging the two different white matter types present in neonates. The probabilistic and geometric anatomical descriptors are then used to compute the transformation $h$ that minimizes the distance between the class posterior images, as well as the distance between surfaces represented as currents. | 52 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

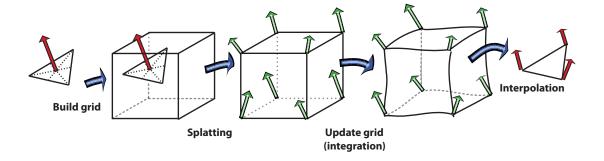

| 3.3  | Particle Mesh approximation algorithm to transform the computation from irregular domain to regular domain based on four basic steps: grid construction, splatting, integration and interpolation                                                                                                                                                                                                                                                                                                                                                                      | 57 |

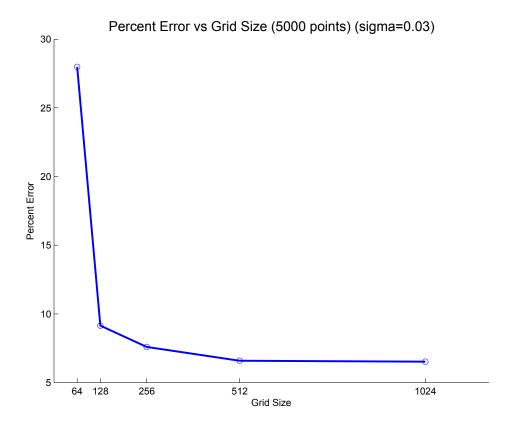

| 3.4  | The percent error for different for 5000 randomly generated points with different mesh sizes                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 58 |

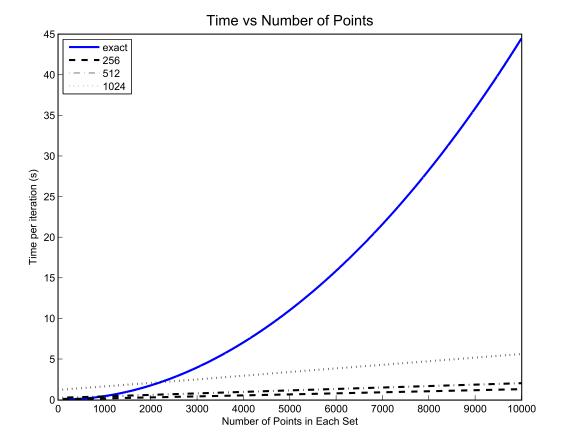

| 3.5  | Run time comparisons between direct computation and the particle mesh implementation for various grid sizes                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 59 |

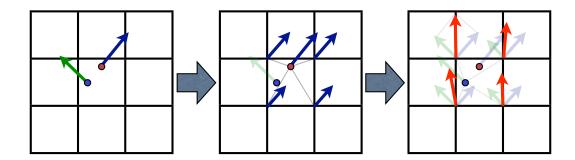

| 3.6  | Geometrical conversion based on a splatting function with zero velocity field $v$ (Eq 3.13). The method served as a bridge to transform the computation from an irregular grid to a regular grid which allows an efficient parallel implementation                                                                                                                                                                                                                                                                                                                     | 61 |

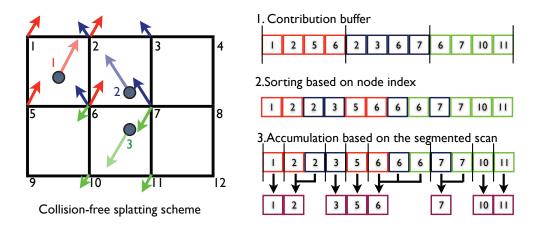

| 3.7  | Collision-free splatting implementation using fast parallel sorting. The method is based on ordering the node contribution ID to resolve resource conflicts which allows a parallel efficient integration based on an optimal parallel prefix scan implementation                                                                                                                                                                                                                                                                                                      | 62 |

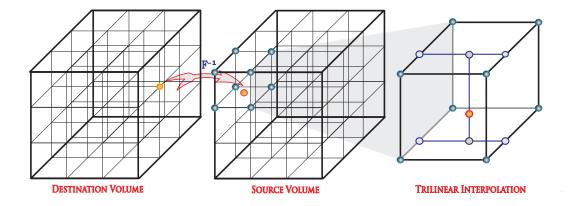

| 3.8  | Reverse mapping based on 3D trilinear interpolation that eliminates the missing data of a forward mapping. The implementation on GPU exploits the hardware interpolation engine to achieve significant speed up                                                                                                                                                                                                                                                                                                                                                        | 64 |

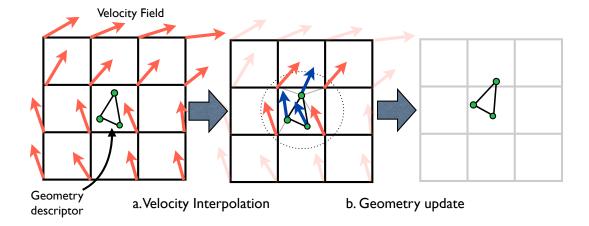

| 3.9  | Geometries are updated through the interpolation from the velocity field. This step maintains the consistency between probabilistic and geometrical compartments of the mixture model                                                                                                                                                                                                                                                                                                                                                                                  | 65 |

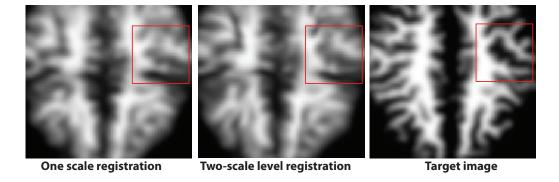

| 3.10 | Multiscale registration using different sizes of computation kernels help capture large and small scale changes in different levels and also increase the convergence rate of the algorithm                                                                                                                                                                                                                                                                                                                                                                            | 66 |

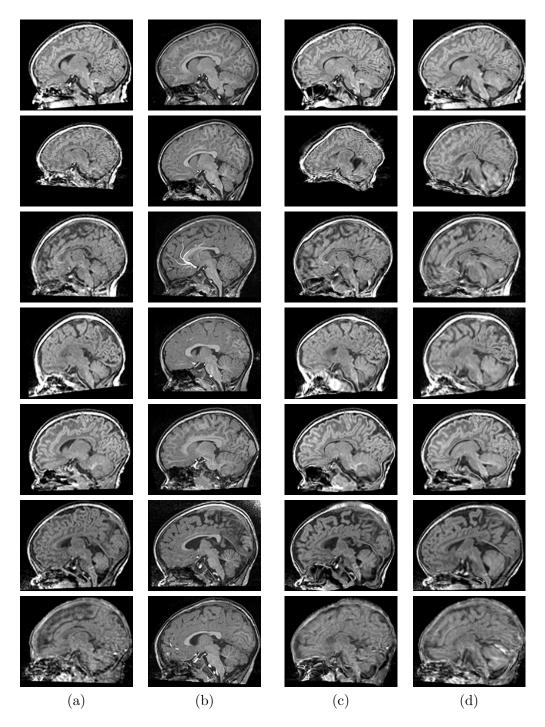

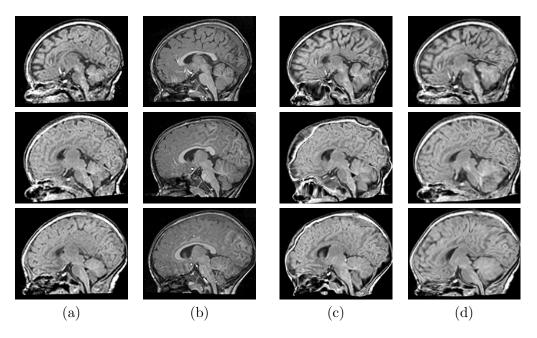

| 3.11 | Registration results of neonates mapped to 2-year-olds. From left to right: (a) neonatal T1 image after affine registration, (b) reference T1 image at 2 years, followed by (c) neonatal T1 after deformable mutual information registration using B-splines, and (d) after combined probabilistic and geometric registration. From top to bottom: subject 0012, 0102, 0106, 0121, 0130, 0146 and 0156                                                                                                                                                                 | 68 |

| 3.12 | Registration results of neonates mapped to 2-year-olds. From left to right: (a) neonatal T1 image after affine registration, (b) reference T1 image at 2 years, followed by (c) neonatal T1 after deformable mutual information registration using B-splines, and (d) after combined probabilistic and geometric                                                                                                                                                                                                                                                       | 60 |

|      | registration. From top to bottom 0174, 0177 and 0180                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 69 |

|      | X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

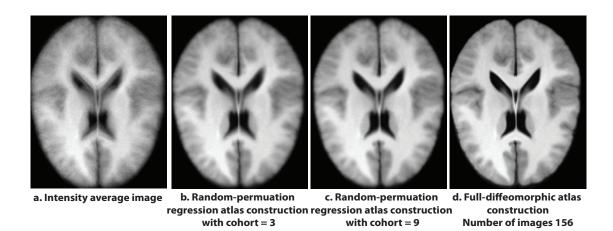

| 4.1  | Atlas construction result on the ADNI data set composed of 156 images sized $144 \times 192 \times 160$ , with different average computations: a) the intensity average and the diffeomorphic atlas constructions with b) random permutation ([56]) with cohort size of 3 images c) random permutation with cohort size of 5 images and d) and all image using our out-of-core streaming framework. It is clear that the ability to compute the atlas using nonlinear diffeomorphic registration with all the image yields a discernible improvement in the quality of the construction |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

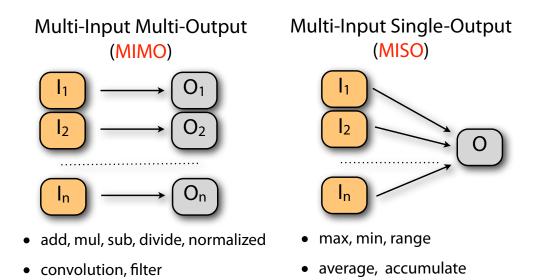

| 4.2  | Basic multi-image operators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4.3  | General MIMO operators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

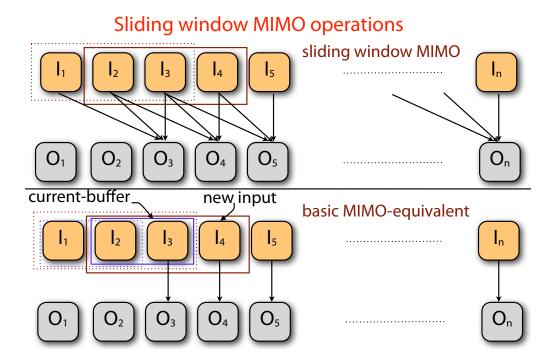

| 4.4  | Sliding window MIMO operators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

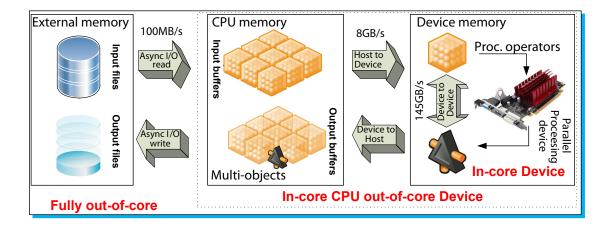

| 4.5  | Overview of data movement in our multi-image processing multilevel out-<br>of-core streaming framework for heterogeneous systems                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

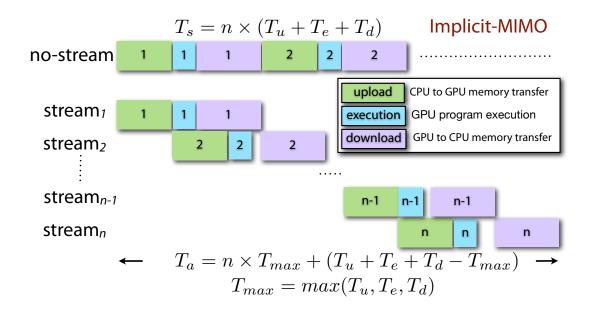

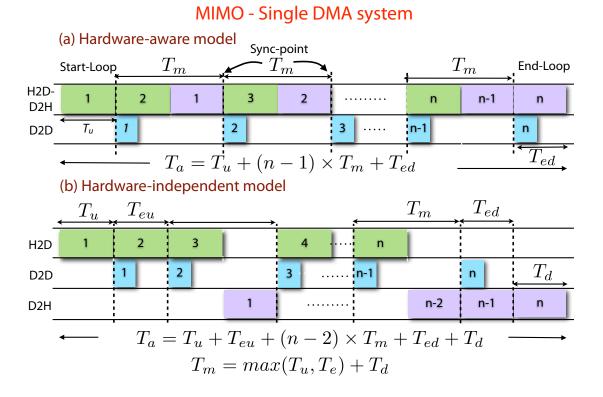

| 4.6  | Implicit processing model for MIMOs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

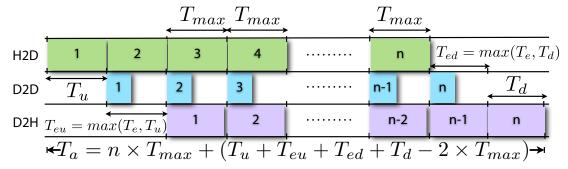

| 4.7  | Pipeline explicit processing model for MIMO operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4.8  | Although the hardware-independent model miss-predicts the system configuration, the performance is still optimal                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4.9  | The transformation from a synchronous model to an explicit streaming model preserves semantic correctness                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

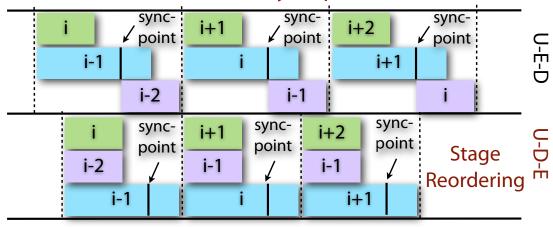

| 4.10 | Streaming optimization using reordering technique. As shown on the figure it is able to eliminate the negative effect of forced-synchronous function 91                                                                                                                                                                                                                                                                                                                                                                                                                                 |

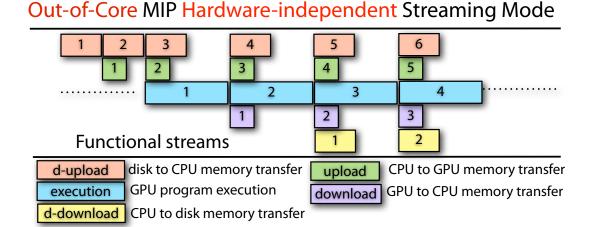

| 4.11 | The implementation of hardware-independent model for "full" out-of-core multi-image processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

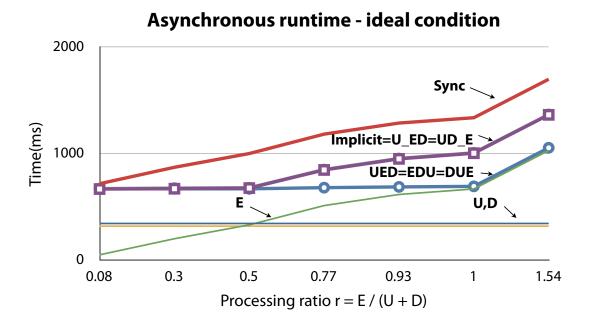

| 4.12 | Runtime comparison of different streaming strategies in ideal conditions. All the permutation of explicit model yield the same performance. The hardware-independent models achieve the optimal performance 93                                                                                                                                                                                                                                                                                                                                                                          |

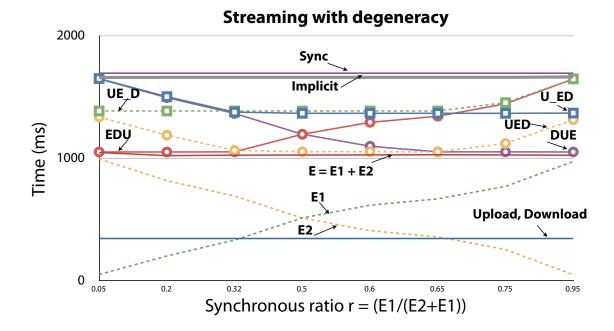

| 4.13 | Runtime comparison of different streaming strategies in degenerate conditions 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

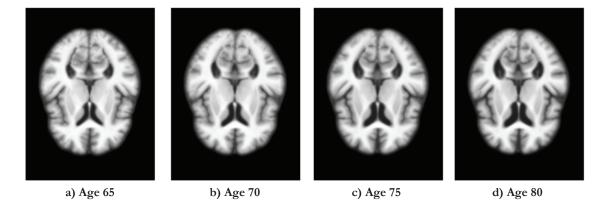

| 4.14 | Age regression anlysis on the ADNI dataset by computing the average brain atlases at different ages (65, 70, 75, and 80) corroborates the hypothesis that fluid space is larger because brains atrophy overtime. This analysis, however, could only be performed if the system is capable of processing the whole dataset of 300 healthy brain-images                                                                                                                                                                                                                                   |

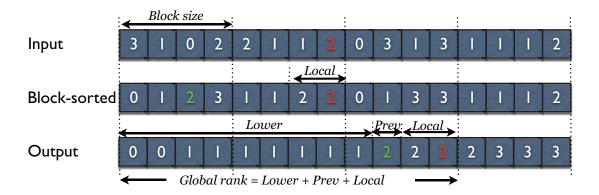

| A.1  | Global ranking computation for block radix sorting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

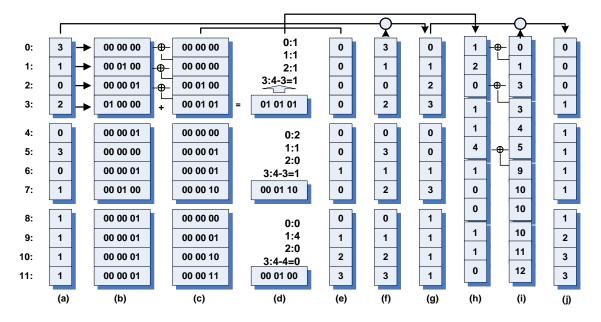

| A.2  | Illustration of our implicit radix sorting (intermediate steps) a) Inputs b) Implicit-presentation of the input c) The local-prefix sum d) Number of each radix bucket e) Number of previous same bucket elements f) local rank g) presorted result h) Number of radix values in each block i) Start offset j) Sorted output                                                                                                                                                                                                                                                            |

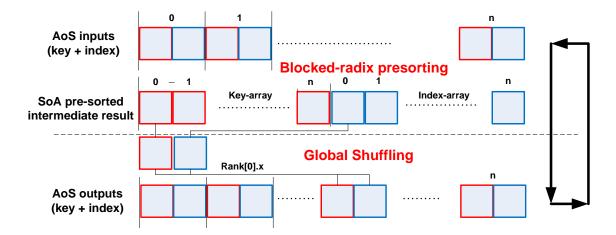

| A.3  | The flow of our hybrid-data format. The conversion occurred implicitly inside the global shuffling kernel and at the beginning of local counting                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | kernel using texture memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

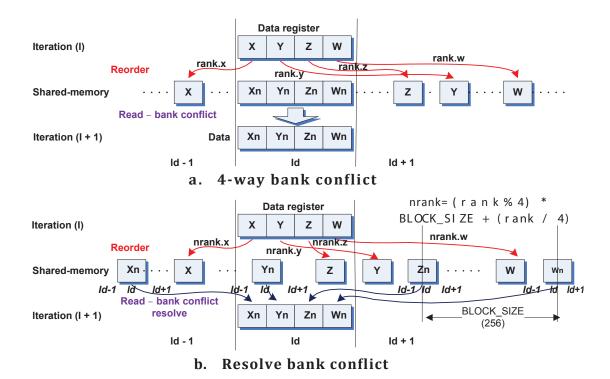

| A.4 | Resolve the 4-way memory conflict                                                                                                                                                                        | 109 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

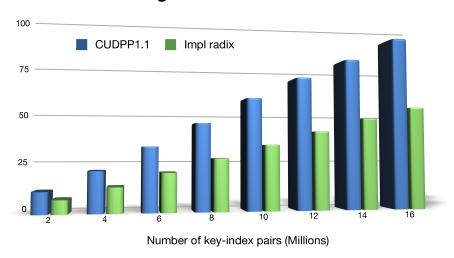

| A.5 | Total run-time of presorting step (ms) with Implicit Radix and Satish CUDPP radix-16                                                                                                                     |     |

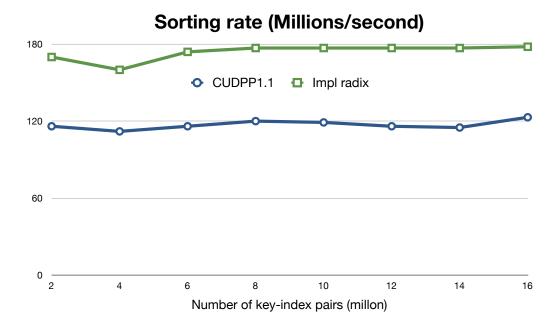

| A.6 | The sorting rate comparison of random 32-bit unsigned inputs                                                                                                                                             | 111 |

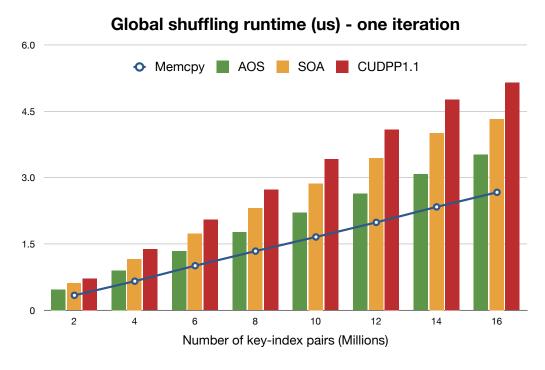

| A.7 | Global shuffling run-time comparison (ns) between our implementation of global shuffling with AoS, SoA structures, and CUDPP1.1 in reference to the device to device memory copy of the same input size: | 111 |

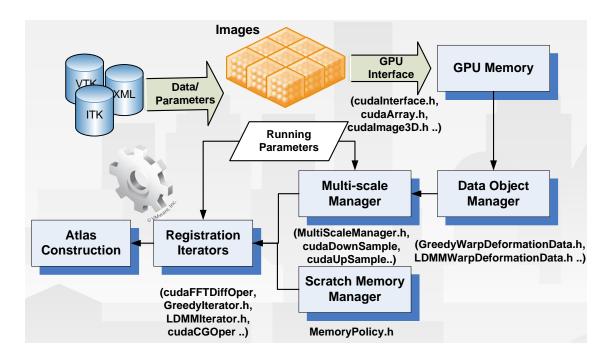

| В.1 | Atlas construction framework data flow architecture overview                                                                                                                                             | 114 |

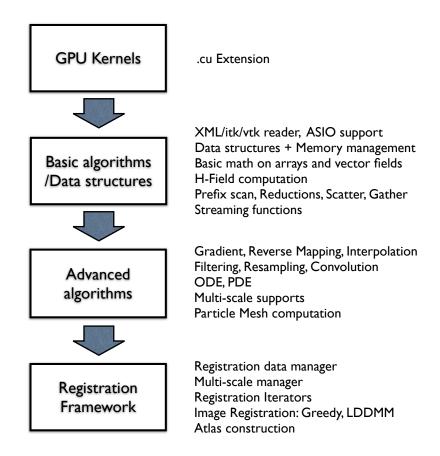

| B.2 | Software development architecture of the AtlasWerk image registration framework                                                                                                                          | 116 |

| В.3 | A sampler of kernel/interface functions, which adds a constant to an array. The function is stored with .cu file extension and is compiled using CUDA compiler                                           | 116 |

| B.4 | C++ template implementation of the multiscale registration                                                                                                                                               | 124 |

# LIST OF TABLES

| 2.1         | Runtime comparison in milliseconds of different gradient computations: simple global memory, linear 1D texture, 3D texture and shared memory approaches                                                                                                                                                | 31  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2         | Runtime comparison in milliseconds of different 3D interpolation implementations for reverse mapping operator using global memory, 1D linear texture and 3D hardware-accelerated texture                                                                                                               | 32  |

| 2.3         | Performance comparison, in GFLOPs, between our implicit method and explicit implementations (larger is faster)                                                                                                                                                                                         | 37  |

| 2.4         | Performance comparison, in milliseconds, between different optimization strategies to implement 3D-Gaussian Filter with different kernel sizes                                                                                                                                                         | 39  |

| 3.1         | Overlap measures comparing the registered segmentation maps against the reference segmentation maps for the parenchyma and cerebellum structure, obtained without deformation (None), deformable mutual information registration (MI), and our proposed method (P+G)                                   | 69  |

| 3.2         | Runtime comparison, in milliseconds, of different splatting implementations on volume sized $144 \times 192 \times 160$ and $160 \times 224 \times 160$ using collision-free sorting approach, atomic operation with fixed point presentation, atomic operation on the shared memory and CPU reference | 71  |

| 3.3         | Time elapsed, in minutes, for registration using deformable mutual information (MI) on the CPU (AMD Phenom II X4 955, 6GB DDR3 1333) and our proposed approach (P+G) on the GPU (NVIDIA GTX 260, 896MB) with 1000 iterations of gradient descent                                                       | 71  |

| 4.1         | Runtime comparison of regular functions with different streaming strategies                                                                                                                                                                                                                            | 95  |

| <b>A</b> .1 | Component runtime comparision, in milliseconds, in one iteration of a 16M-pair input between our implicit sorting and the Satish <i>et al.</i> implementation.                                                                                                                                         | 110 |

#### ACKNOWLEDGEMENTS

What does the creator of a dissertation aspire to? Of course, to fulfill academic requirements for a Ph.D., but this is not the only goal. Maybe some want to prepare for an academic career, and some want to impress their peers or their parents. My aspiration is to present a dissertation that does not only make a small but significant contribution to scientific development, a system that not only provides functionality, flexibilities and powers to developers but also has a significant impact on practical applications.

The most important reason for succeeding is the guidance and support which I received from my advisor, Claudio T Silva. I have learned immensely from him. He taught me how to find direction in Ph.D. thesis work, drill down to the essentials, and make a dissertation out of it. I am highly grateful to him for making my Ph.D. thesis work such a smooth and rewarding experience.

The other committee members, Sarang Joshi, Jens Kruger, Joao Comba and Thomas Fletcher, are not only my mentors and co-workers but also my friends. They have given me tremendous help and advice. I find myself a lucky person who had the chance to work directly with all committee members. It makes my dissertation process a pleasant experience. Sarang Joshi, my co-advisor, has brought me a different research viewpoint from the image processing community. Sarang has also taught me how to derive and construct a solid foundation for my research based on mathematical analysis. Jens Kruger worked together with me in almost all submissions. Jens is always available to share experience, to understand the difficulties that I meet, and to give me tireless support from the beginning of my research. I could not complete my thesis work without guidance and encouragement from Jens. Though the amount of time I worked with Joao Comba and Tom Fletcher was less than with the others, it always brought me great experience. I have learned from them not only the knowledge but also methodologies to do research. They gave me beautiful advice and helped me grow in my academic development. I'm very glad that Joao has come to work at our institute in this critical period of my research.

I'm very grateful to have the chance to do summer internships at the Deep Computing group at the IBM Watson research center in 2007 and at the Quantitative Visualization

Group of ExxonMobil Upstream Research company in 2009. My mentors at IBM: James Klosowski and Wagner Correa and my mentors at ExxonMobil: Dominique Gillard and Mark Dobin are the most excellent mentors who brought me working environment, research challenges, and a handful of industry experience that I could not have had in the academic environment. The idea of a dissertation work with significant research implications has originated during my internship in the industry where the importance of research is not only measured by its novel content but how it influences the research of co-workers.

Also, very important to this work is the supportive environment I found at Scientific Computing and Imaging Institute (SCI) where I worked until the end of May 2010. I appreciate my colleagues' interest in my work and their moral support, for which I would like to thank them very much. In particular, the creative atmosphere in the Visualization and Geometric Computing (VGC), originally with Huy Vo, Emanuele Santos, Carlos Scheidegger, John Schreiner, Steve Callahan, Erik Anderson, Louis Bavoil and later with Tiago Etiene supported my ascent to prevail with this dissertation. I wish to thank them all. I have collaborated with many people over the last years. In one way or another, they have influenced my thinking. Particularly important are the discussions I had with Marcel Prastawa, Guido Gerig, Thomas Fogal, and Sam Preston. I would like to thank them very much. In a similar vein, I would like to thank Nikhil Phatak and Le-Thuy Tran. I want to give special thanks to Thomas Fogal for his persistent support on revising the content and writing of not only the thesis but also other research submissions. Tom is always the first, critical reviewer who helps improve the writing as well as the technical content to make our papers strong submissions.

Last but not least, I want to express my appreciation and thankfulness to my parents and my brother in my home country who give me constant spiritual and financial support from the beginning of my PhD. Thanks to my Vietnamese friends at the University of Utah: Anh Vo, Hoa Nguyen, Huong Nguyen, Khiem Nguyen, Trang Pham, Thanh Huynh and many others, who bring me my home culture and beliefs, share happiness and difficulties with me, and provide me balance outside the academic life, which I see as indispensable factors for my academic success. For that I wish to thank them all.

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Parallel computing overview

Parallel computing has transformed a number of science and engineering disciplines, including cosmology and astrophysics, environmental and climate modeling, plasma and condensed matter physics, bioinformatics and computational biology, quantum chromodynamics, device and semiconductor simulation, seismology, turbulence, societal health and safety, earthquakes, geophysical exploration and geoscience, materials science and computational nanotechnology, human/organizational system studies, stockpile stewardship, signals intelligence, defense, etc. [4, 7, 92] (Figure 1.1).

For example, consider cosmology and astrophysics, the study of the structure and evolution of the universe, where one of the most striking paradigm shifts has occurred. A

**Figure 1.1.** Parallel computing has been a driving force for the development of many scientific research disciplines and the solution for a number of engineering challenges in domain as diverse as mechanical engineering, nuclear physics, bio-science, applied physics, weather prediction, astronomy, geology, and more (Image courtesy of Blaise Barney, Lawrence Livermore National Laboratory [7])

number of new, tremendously detailed observations deep into the universe are available from such instruments as the Hubble Space Telescope <sup>1</sup> and the Digital Sky Survey. <sup>2</sup> However, until recently it has been difficult, except in relatively simple circumstances, to tease enough information from mathematical theories of the early universe to allow comparison with observations. Massively parallel computers with large memories, however, have changed all of that. Today, cosmologists can simulate the principal physical processes at work in the early universe over space-time volumes sufficiently large to determine the large scale structures predicted by theoretical models [42, 112]. With such tools, some theories can be discarded as being incompatible with observations [6]. High-performance computing has allowed comparison of theory with observation and thus has transformed the practice of cosmology.

Another example is bioinformatics and computational biology [129], especially in molecular biology, which seeks to understand how cells and systems of cells function, with the goal of improving human health, longevity, and the treatment of diseases. Computer simulations remain the only approach to understand the dynamics of macromolecules and their assemblies. Understanding the characteristics of protein interaction networks and protein-complex networks formed by all the proteins of an organism requires tremendous computational resources. Even when knowledge-based constraints are employed, the protein-folding problem—computational modeling and prediction of protein structures to understand the mechanism that translates gens into proteins—remains computationally intractable.

The complexity of molecular systems, in terms of both the number of molecules and the types of molecules, demands computation to simulate and codify their logical structure [104, 116]. There has been a paradigm shift in the nature of biological computing with the decoding of the human genome and with the technologies this achievement enabled. Equations of physics-based computation are now complemented by massive-data-driven computations and heuristic biological knowledge. In addition to the deployment of statistical methods for large data processing, a countless number of data mining and pattern recognition algorithms are being developed and employed [25, 125]. Finding multiple alignments in the sequences of hundreds of bacterial genomes is a computational

<sup>1</sup>http://www.nasa.gov/mission\_pages/hubble/main/index.html

<sup>&</sup>lt;sup>2</sup>http://archive.stsci.edu/cgi-bin/dss\_form

problem that can be attempted only with novel alignment algorithms on peta-scale supercomputing resources [3, 9]. Large-scale gene identification, annotation, and clustering expressed sequence tags are other large-scale computational problems in genomics [40].

The capability to perform predictive simulations of biochemical processes transform our ability to understand the chemical basis of biological functions. This greatly improves our ability to design new therapeutic drugs, treat diseases, and understand the mechanisms of genetic disorders in addition to its value in basic biological research.

All the experiences from the development of super computing in the late twentieth century as well as hybrid computing in the recent ten years [114] have taught us the importance of building a firm scientific foundation using scalable, parallel computing, which allows us to expand and validate mathematical theories, and to compare simulation experiment and observation. We also have learned that the consistency of the programming model more than the intricacies of the hardware led us to the target. Parallel computing now has a big influence on everyday life and research by providing more accurate, detailed, and trusted predictions. However, moving entire research disciplines to the parallel computing world has imposed significant challenges.

#### 1.1.1 Modern trends in parallel computing

The improvement of processing power has been driven by the Moore's Law [86] which predicts a long term development of fabrication techniques that doubles transistor density every two years. Nowadays, after more than four decades, the principle is still going strong [68]. Though this tendency is likely to be kept for another decade or more the ever-increasing transistor density no longer delivers comparable performance improvements. Adding transistors adds wire delays and speed-to-memory issues. More aggressive single-core designs lead to greater complexity and heat. Furthermore, scalar processors themselves have a fundamental limitation: a design based on serial execution, which makes it extremely difficult to extract instruction-level parallelism from application codes.

These issues are no longer the concern of only high-end users. It is becoming more apparent that major performance improvements could have a profound effect on virtually every scientific field. The demands for trans-petaflop systems require the development of new strategies to augment Moore's Law and to explore innovative High Performance Computing (HPC) architectures that can work around the limitations of conventional systems. These strategies include:

- *Multicore systems* that fabricate two or more cores on a die to continue providing steady performance gains.

- Specialized processors that enhance performance in areas where conventional models are inadequate.

- Heterogeneous computing architectures, in which conventional and specialized processors work cooperatively.

Each of these strategies can potentially deliver substantial performance improvements.

#### 1.1.1.1 Multicore systems

Placing multiple cores on a die is the fastest way to deliver continuous performance gains in line with Moore's Law. Well-known examples of multiple-core processors are the AMD Opteron [69] and the Intel Xeon [103]. This strategy offers immediate multiple factors of computing density, while reducing per-processor power consumption and heat.

Although multicore processing provides a steady performance gain for many applications, especially those requiring heavy floating-point operations, for other applications which depend on heavy bit manipulation and/or massive data bandwidth such as sorting, signal processing, database searching, data encryption/decryption, improvement of the raw computational power is not enough. These applications often require speeds and memory bandwidth in orders of magnitude beyond what are available today through conventional processors [53]. It is unlikely that the benefit of having multiple fully generic processing cores will grow at the same rate as the transistor integration.

#### 1.1.1.2 Specialized processors

In recent years, architectures based on clusters of commodity processors have overtaken high-end, specialized systems in the HPC community due to their low cost and solid performance for many applications. However, as users begin to experience the inherent limitations in terms of scalability of scalar processing, we are beginning to see a reversal in that trend [64, 114]. Examples of this resurgence include:

- *Vector processors*: vector processors increase computational performance by efficiently pipelining identical calculations on large streams of data, eliminating the rate limitation of instruction of conventional processors [64].

- Multithreaded processors [121]: the memory speeds have been increasing at only a fraction of the rate of processor speeds, leading to performance bottlenecks as

serial processors wait for memory. Systems incorporating multithreaded processors such as Intel's Hyper-Threading [79] address this issue by modifying the processor architecture to execute multiple threads simultaneously, while sharing memory and bandwidth resources to increase the memory bandwidth utilization.

- Digital Signal Processors (DSPs): DSPs are optimized for processing a continuous signal, making them extremely useful for audio, video and radar applications [110]. Their low power consumption also makes these processors ideal for use in plasma TVs, cell phones and other embedded devices.

- Specialized coprocessors: coprocessors such as graphic processing units(GPUs), n-body accelerator such as GRAPE, and FPGAs use multi-simple-core array processor architectures to provide a large number of arithmetic logical units and floating-point components (multiply/add units) per chip. They can deliver noticeable improvements on mathematically intense functions, such as multiplying, inverting matrices, and visualization.

Processors such as these can deliver substantially better performance than generalpurpose processors for some operations. Vector and multithreaded processors are also latency tolerant and can continue executing instructions even when large numbers of memory references are simultaneously underway. These enhancements can allow significant application performance improvement, while reducing intercache communication burdens and real estate on the chip required by conventional caching strategies.

Since specialized processors have traditionally been deployed, they have had serious limitations. Although they can provide excellent acceleration for some operations, they often run scalar code much slower than commodity processors. However, most software used in the real world employs at least some scalar code. Furthermore, these processors traditionally have been incorporated into more conventional systems via the PCI bus-as a peripheral. The inadequate communication bandwidth severely limits the acceleration that can be achieved. Communicating a result back to the conventional system may actually take more time than the calculation itself.

There are also hard economic realities of processor fabrication. Unless the processor has a well-developed market niche that will support commodity production, such as the applicability of DSPs to consumer electronics, few manufacturers are willing to take on the large cost of bringing new designs to market.

These issues lead us to alternative models such as heterogeneous computing models. While it turns out to be very close to the specialized processor model, it attacks the latency and bandwidth issues while allowing mass production support in the guise of graphics processing units.

#### 1.1.1.3 Heterogeneous computing

Heterogeneous computing is the strategy of deploying multiple types of processing units within a single workflow. Each unit performs the tasks to which it is best suited. The model employs specialized processors to accelerate some operations to several magnitudes faster than what scalar processors can achieve, and at the same time it expands the applicability of conventional microprocessor architectures. Different from specialized processor models, heterogeneous models tightly couple processing elements in a single system to exploit the high performance communication bridges to connect between them, significantly reducing the latency between computation units and commodity control hardware.

The main advantage of this model is that HPC applications typically include both code that benefits from acceleration and code that is suited for conventional processing. While there is not a single type of processor that is best for all computations, heterogeneous processing models allow better utilization and performance by using the right processor types for each operation.

Traditionally, there have been two primary barriers to widespread adoption of heterogeneous architectures: the programming complexity required to distribute workloads across multiple processors and the additional effort to communicate between processors of different types. These issues can be substantial, so any potential advantages of a heterogeneous approach must be weighed against the cost and resources required to overcome them.

Nowadays, the rise of multicore systems has already created technology demands that largely change the programming perspective of the HPC software developer, opening the door to new programming strategies and environments. As software designers become more comfortable programming on the multiprocessor platform, they are willing to consider other types of architectures, including heterogeneous systems.

There are several new heterogeneous systems emerging recently. The Cray X1E supercomputer, for example, incorporates both vector processing and scalar processing. The Cell processor architecture (designed by IBM, Sony and Toshiba to accelerate gaming

applications on the new Playstation 3), uses a conventional processor to offload computationally intensive tasks to synergistic processing elements with direct access to memory. Field Programmable Gate Arrays (FPGAs), hardware-reconfigurable devices that can be redesigned to solve specific types of problems efficiently, are attracting strong interests to use as reconfigurable coprocessors [66]. However, the most exciting areas of heterogeneous computing emerging today employ Graphic Processing Units, or GPUs.

#### 1.1.2 Parallel computing challenges

The increase in the accuracy, detail and volume of observation data requires a hand-inhand development of high performance computing. The moving of the computation from 2D to 3D, even to n-D has demanded not only massive computing power but also novel parallel caching techniques and sophisticated bandwidth strategies. Parallel computing requires the development of advanced data preprocessing, data compression, out-of-core processing, message-passing, and compiling techniques to ease this transition.

Porting code to parallel architecture is much more than simply bringing up an existing code to a new machine [21, 24, 58]; it often presents an opportunity to reformulate the basic code and data structures, more importantly to reevaluate the basic representation of the data or the mapping of the algorithm and its efficiency on the new architecture.

To become a successful high-end technology, a persistent programming model for scalable, parallel computers is essential. This means providing a stable effective programming model over the life time of the application. Application developers need principles and tools that would survive in the long term and isolate them from the changing nature of underlying hardware. On the other hand, they also need the capability to exploit new hardware features and new parallel algorithms. This is even a challenge with the conventional parallel computing model. The software development on supercomputers, for instance, is often highly optimized for specific models, and requires entire code revision to adapt to new hardware. The principal goal of high performance computing has been the development of software and algorithms that address the programmability, portability, and flexibility of parallel applications [43, 34].

However, the expression of an explicit parallel programming models is difficult. The developers often have to specify not only how to partition data and computation among processors but also the data movement and synchronization to achieve high performance and to ensure correctness. Besides, portability is hard to define and difficult to achieve. Different application programming interfaces come from different vendors without a cross-

platform standard, making it tedious to convert the program to run on new platforms. However, portability is not a just a matter of a common interface. Though it is possible to express the program in a reasonably machine independent way, this increased portability often comes at the price of performance. The ability to achieve the highest performance possible on each machine from the same program image, *portable performance*, is a very important topic in the science of parallel computing [90].

In addition, the algorithms themselves are not always portable. To achieve the highest performance, algorithms often need to select a different parameterization specific to the machine it will run on. The changing in the parallel granularity, memory hierarchy and bandwidth, and also caching strategies makes portable programming even more difficult.

Another challenge comes from the complexity of the problems which requires different and extraordinary skills from the application developers. Often it means multiple programming paradigms, and multiple programming languages potentially must co-exist. Interoperability is an indispensable consideration of parallel computing and also a challenge in designing parallel computing languages.

The success of a parallel computing model depends on how sufficiently it addresses these challenges. This explains the convergence in HPC computing to unified architecture and programming models [117] and why hybrid computing, especially GPU computing, is emerging as a major trend in the parallel processing community, gradually replacing conventional computing models.

## 1.2 GPU computing

A graphics processing unit is a specialized coprocessor that offloads and accelerates 3D or 2D graphics operations from the central processors. There are two primary forms of GPUs: the discrete video cards and those integrated on the main system. In either form, the GPU is an essential, indispensable component of many commodity systems. GPUs have been using in embedded systems, smart phones, personal computers, game-consoles, workstations, etc. [39, 73, 89, 92, 101]. The orthodox appearance is the biggest advantage of GPUs over other specialized coprocessors and secures mass production support, research attention and constant technical improvement.

GPUs started as fixed-function graphic accelerators (Figure 1.2.a), which contain special mathematical operations and a number of graphics primitive operations commonly used in rendering [36]. Over the years, GPUs have become increasingly more powerful

**Figure 1.2.** The development of GPU processing pipeline from a) a fixed function pipeline to b) a programmable pipeline is a prerequisite for General Purpose Computing on GPUs (GPGPUs).

and programmable with demands to support complex and high-quality scientific visualization [97, 96]. Nowadays, GPUs can deliver up to a teraflop of computing power from the same silicon area as a comparable microprocessor using a small fraction of the power per calculation: higher performance in a smaller footprint, at a lower cost, and using less power. The ability to drive raw computational power and memory bandwidth equivalent to supercomputers in the mid-90s on commodity devices makes GPUs an attractive approach to bring supercomputing power to regular users and to uphold Moore's Law.

In the early 2000s, computer scientists along with researchers in medical imaging and electromagnetics started using GPUs for running general purpose computational applications [85, 119]. They found the excellent floating point performance in GPUs led to a huge performance boost for a range of scientific applications. This was the advent of the movement called GPGPU or General Purpose computing on GPUs [77]. The initial attempts had defined the potential and essential functionality to transform GPUs from specialized coprocessors to more general purpose HPC units.

However, GPUs have had their own historical barriers to widespread adoption. First, they traditionally have been integrated into conventional systems via the PCI bus, which limits their effectiveness compared to other specialized processors mentioned above. More critically, the difficulty in mapping scientific algorithms and data structures to the ren-

dering of graphical primitives is a major obstacle for its use in general HPC problems. Fortunately, for the attractiveness of the raw computational power provided by modern GPUs and the popularity of GPUs in visualization, graphic programming languages such as OpenGL, CG and DirectX have been widely accepted by application programmers, including GPGPU developers.

Graphic vendors have realized the potential to bring this performance to a larger research community and invest in redefining GPU architectures, providing the fully programmable capability and development support for scientific applications [5, 91, 117]. The adoption of high-level languages such as C, C++, and later FORTRAN, the introduction of unified parallel programming models (CUDA, OpenCL, Direct Compute) make it easier for HPC developers to access the GPU computing potential.

The development of the communication channel between GPUs and conventional processors has increased the transfer bandwidth and significantly reduced the data latency. Starting with the introduction of Accelerated Graphic Port (AGP) from 1997 [38], an alternative of PCI bus - a dedicated pathway between a slot and conventional processors, APG 3.5 was capable of delivering transfer rate up to 2.133 Mbps. In 2004, AGP was replaced by PCI express (PCIe) [22]. PCIe 3.0 standard hardware is capable of 16 Gbps transfer rate almost equivalent to the CPU memory bandwidth. In addition to a dedicated communication path between devices, modern GPUs allow an asynchronous execution model that overlaps between computation and data transfer, an effective mechanism to hide the data transfer latency from the computation.

Consequentially, GPUs have been widely adopted in HPC community, increasingly being used to accelerate a wide range of science and engineering applications, in many cases offering dramatically increased performance in comparison to CPUs. In practice, GPUs can compute 100x faster than even the fastest general-purpose processors for some computational problems. Significant biomolecular, computational chemistry, astrophysical, condensed matter physic, weather modeling and seismic stack migration applications have already benefited substantially from or show substantial promise for using GPUs [12, 73, 104].

#### 1.2.1 GPU computational model

GPUs are regarded as high-throughput processors that can achieve theoretical peak performance of several tera-flops. GPUs operate on an SIMT (single-instruction multiple thread) basis where thousands of light weight threads execute the same instruction simultaneously. Much like the SIMD processor, GPUs, however, allow different levels of SIMD execution that only require all cores in the same group (*multiprocessor* or a *wavefront*) execute the same instruction at the same time. Different groups could execute different (or the same) instructions. Furthermore, SIMT handles conditionals somewhat differently than SIMD, where some cores are disabled for conditional operations.